Innesco RS Il principio di funzionamento del trigger RS. schema

RS-trigger è una semplice macchina di controllo, solitamente implementata sotto forma di circuito elettronico digitale, appartenente alla classe dei circuiti sequenziali. Come è noto, nei circuiti digitali, i dispositivi funzionali di tipo sequenziale includono registri, contatori, generatori di numeri e automi di controllo, compresi i trigger di vario tipo.

Posiziona i trigger nei circuiti digitali

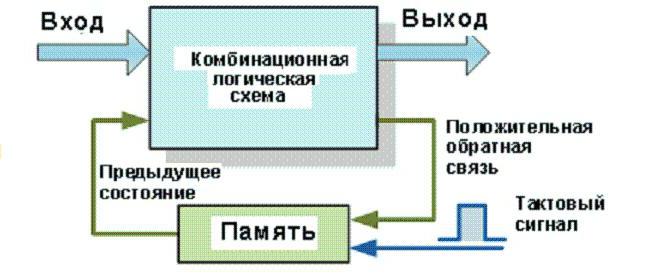

A differenza dei circuiti logici combinatori, che cambiano stato in base ai segnali effettivi applicati ai loro ingressi in un determinato momento, la logica sequenziale ha una qualche forma di "memoria" intrinseca incorporata, in modo che possano prendere in considerazione sia lo stato precedente che quello reale dei loro input ed esce. Di seguito è mostrato lo schema a blocchi generale del dispositivo sequenziale.

Il trigger RS come automa di controllo digitale include la memoria effettiva e il circuito di controllo combinatorio su elementi linguistici tipici che implementano il suo algoritmo logico di input. Se consideriamo questo circuito come applicato ai circuiti di trigger più semplici, allora non hanno una memoria strutturata sotto forma di una sorta di microcircuito specializzato o nodo circuitale. La memoria trigger esiste al livello della funzione, come se fosse incorporata nell'algoritmo del suo schema di controllo combinatorio. La manifestazione di questa "memoria" è la cosiddetta bistabilità di un trigger, le cui uscite possono essere in uno dei due stati fondamentali: un'unità logica (in seguito - 1) o uno zero logico (in seguito - 0). Il trigger memorizza i valori di stato stazionario delle sue uscite ("scatta") e salva finché non si verifica il successivo cambiamento nei suoi segnali di ingresso.

classificazione

Se gli elementi logici standard sono gli elementi costitutivi dei circuiti combinatori, i circuiti bistabili, incluso il flip-flop RS, sono i componenti principali della costruzione di dispositivi logici sequenziali, come registri di memorizzazione dati, registri a scorrimento, dispositivi di memoria o contatori. In ogni caso, i trigger considerati (ovviamente, come tutti i circuiti sequenziali) possono essere fatti dei seguenti tipi di base:

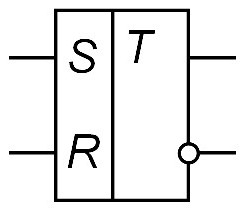

1. Trigger RS asincrono - un circuito che cambia stato immediatamente quando cambiano i segnali di ingresso. Per il tipo di dispositivi in questione, sono i segnali agli ingressi di informazione R (reset) e S (installazione). Secondo la pratica consolidata, gli ingressi corrispondenti sono chiamati come i segnali su di essi.

2. Trigger RS sincrono, controllato staticamente , il cui lavoro è sincronizzato con il livello di un particolare segnale di clock.

3. Il trigger secondo la rivendicazione 2 con controllo dinamico , che è sincronizzato con i momenti dell'apparenza dei fronti (o decadimenti) del segnale di orologio.

Pertanto, se le variazioni di stato delle uscite si verificano solo in presenza di un segnale di clock, che viene alimentato a un ingresso di clock C separato, allora il trigger è sincrono. Altrimenti, il circuito è considerato asincrono. Per mantenere il suo stato attuale, i circuiti sequenziali usano la retroazione, cioè trasferendo una porzione del segnale di uscita al suo ingresso.

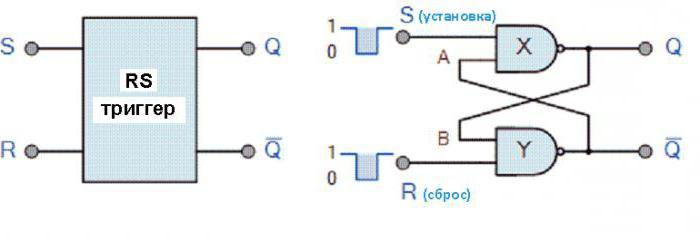

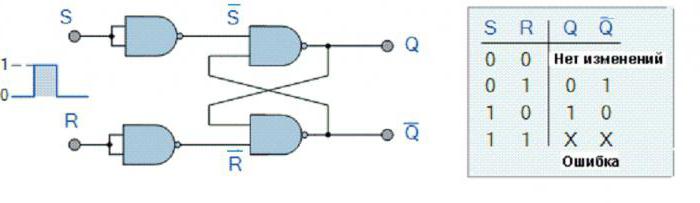

RS-trigger su elementi logici

Il modo più semplice per farlo è unire una coppia di elementi logici NAND a due ingressi. In questo caso, il feedback dall'output di un elemento viene inviato all'ingresso di un altro (vedere lo schema seguente).

Di norma, in questo schema, i segnali di ingresso sono mostrati come inversi (con un trattino basso), sebbene in seguito nell'analisi del lavoro, venga utilizzata la notazione degli ingressi diretti (non invertiti). Questo rende molto difficile capire la logica del trigger. Pertanto, non introdurremo l'inversione degli input nella fase di considerazione dell'operazione del circuito sugli elementi della NAND, ma ne terremo conto in futuro quando verrà modificata.

Quanti ingressi e uscite ha il trigger RS? Si può vedere dal diagramma sopra che contiene un ingresso S e un ingresso R, che servono, rispettivamente, per impostare e resettare il circuito, così come le uscite Q dirette e inverse. Ma questo trigger più semplice si riferisce al tipo asincrono, il suo simbolo è mostrato sotto.

Nel dispositivo sincrono c'è anche un ingresso C per gli impulsi di clock.

Stato "Installato"

Consideriamo come funziona l'RS-flip-flop in questo stato, dato dai valori R = 0 e S = 1. Poiché l'ingresso 0 dell'elemento AND-NO Y è il livello 0, quindi Q = 1 (logica AND-NO). Dall'uscita Y, il segnale Q viene anche ricondotto all'elemento X (ingresso "A"). Poiché S = A = 1, quindi Q = 0.

Se R = 1 è impostato, e l'ingresso S è ancora 1, allora agli ingressi Y abbiamo B = 0 e R = 1, e il suo output è Q = 1, cioè non è cambiato. Quindi, se S = 1, lo schema RS del trigger "scatta" nello stato "Installato" Q = 0 e Q = 1 e cambiando il segnale R non lo cambia.

Stato "Ripristina"

In questo secondo stato stazionario, Q = 0 e Q = 1, ed è definito dagli ingressi R = 1 e S = 0. Poiché l'elemento X ha un ingresso S = 0, il suo output è Q = 1 (logica AND-NOT). Il segnale Q viene ricondotto all'elemento Y (ingresso "B"), e poiché R = B = 1, quindi Q = 0.

Se S diventa uguale a 1 quando R = 1, allora Q rimane uguale a log 0, cioè, non cambia. Quindi, con R = 1, il circuito di trigger viene nuovamente "bloccato" nello stato "Reset" Q = 0 e Q = 1, salvato con qualsiasi segnale S.

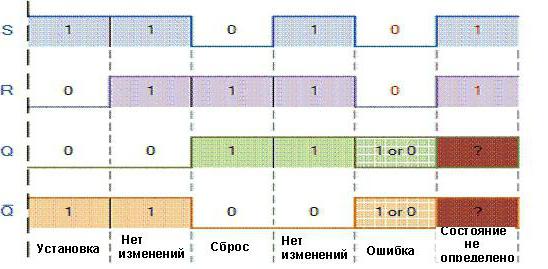

Riassumiamo i risultati nella tabella

Possiamo determinare lo stato dei segnali Q e Q usando la seguente tabella di verità:

| stato | S | R | Q | Q | descrizione |

| installazione | 1 | 0 | 0 | 1 | Uscita Q = 1 |

| 1 | 1 | 0 | 1 | nessun cambiamento | |

| reset | 0 | 1 | 1 | 0 | Uscita Q = 0 |

| 1 | 1 | 1 | 1 | nessun cambiamento | |

| inammissibile | 0 | 0 | 1 | 1 | stato di errore |

Si può vedere che quando S = R = 1, Q e Q possono essere uguali a 1 o 0 (ma non simultaneamente!) A seconda dei livelli degli ingressi S o R prima del verificarsi di questo stato delle uscite. Pertanto, nella condizione S = R = 1, lo stato delle uscite Q e Q non può essere modificato. Può cambiare solo se si modifica il livello da 1 a 0 su uno degli input.

Il valore S = R = 0 è una condizione indesiderabile o inaccettabile e dovrebbe essere evitato. Lo stato S = R = 0 fa sì che entrambe le uscite Q e Q siano impostate al livello 1, mentre lo stato Q dovrebbe sempre tornare a Q. Il risultato è che il trigger perde il controllo su Q e Q e se due ingressi ora vanno in stato 1, il circuito diventa instabile e passa a uno stato indefinito.

RS-Trigger Switch Chart

Quanto è stato detto nella sezione precedente è illustrato dal seguente schema di commutazione.

Come si può vedere, quando S = R = 0, si verifica uno squilibrio (incertezza) dello stato delle uscite. Può portare alla commutazione di una delle uscite più velocemente dell'altra, in conseguenza della quale il trigger passerà a uno o all'altro stato, che potrebbe non coincidere con quello richiesto, e i dati saranno danneggiati. Questo stato instabile viene solitamente chiamato meta-stabile.

Quindi, un simile trigger-latch può essere trasferito nello stato "Installato" archiviando 0 sul suo ingresso S (se c'è 1 sull'ingresso R) e trasferito nello stato "Reset" applicando 0 all'ingresso R (se c'è 1 su S-input). Un trigger entra in uno stato indefinito (meta-stabile) se il livello 0 è simultaneamente applicato a entrambi i suoi input.

La commutazione dello stato delle uscite avviene con un piccolo ritardo rispetto a un cambiamento nel segnale su uno degli ingressi senza utilizzare un segnale di clock. Pertanto, lo schema sopra riportato è un trigger RS asincrono.

Modifica lo schema di trigger

Come abbiamo visto sopra, gli elementi di base dell'IS-NOT del flip-flop RS considerato funzionano in modo tale che quando è impostato, Q = 1 e Q = 0 e quando viene resettato, Q = 0 e Q = 1, anche se sarebbe più logico avere Q nel primo stato = 1, e nel secondo - Q = 0. In questo caso, si scopre anche che il cambiamento di stati si verifica quando il livello del segnale scende da 1 a 0.

Pertanto, per il corretto funzionamento del circuito di trigger, i suoi segnali di ingresso devono essere invertiti. Quindi la commutazione dei suoi stati si verifica quando si applicano segnali di input positivi. Per fare ciò, aggiungi due ulteriori elementi IS-NOT al circuito, collegati come inverter agli ingressi S e R, come mostrato nella figura seguente. Qui, gli ingressi degli elementi AND-NOT rappresentavano già segnali di ingresso inversi.

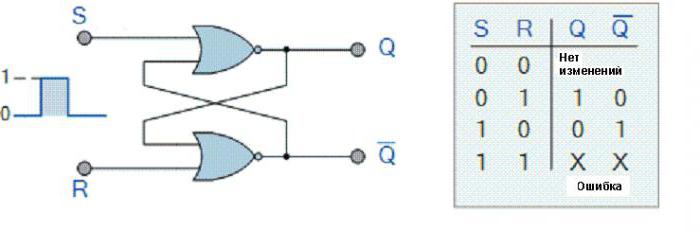

Proprio come con l'uso di elementi AND-NOT, puoi creare un semplice trigger RS utilizzando due elementi OR-NOT collegati allo stesso modo. Funzionerà allo stesso modo dello schema NAND discusso sopra. Allo stesso tempo, un alto livello di segnali sugli ingressi è attivo e si verifica una condizione inaccettabile quando il livello logico "1" viene applicato ad entrambi gli ingressi, come mostrato nella tabella di verità nella figura sottostante.

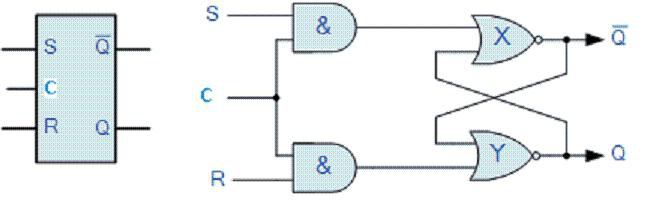

Come sincronizzare il trigger

A volte è desiderabile avere un trigger bistabile in circuiti logici sequenziali che cambi il suo stato quando vengono soddisfatte determinate condizioni, indipendentemente dallo stato degli ingressi S o R. Tale schema può essere creato collegando un elemento a due ingressi AND in modo sequenziale con ciascun ingresso di trigger. Combinando i due input degli elementi E otteniamo il nuovo input del trigger. Aggiungerlo significa che le uscite Q e Q "cambiano lo stato quando il segnale su di esso è alto e, quindi, può essere usato come ingresso C di clock, come mostrato nella figura sotto.

Quando il segnale all'ingresso C è a livello 0, le uscite dei due elementi And sono anche a livello di 0 (la logica dell'elemento And), indipendentemente dallo stato dei due ingressi S e R, e le due uscite Q e Q sono "bloccate" nell'ultimo stato stazionario. Quando il segnale sull'ingresso C passa al livello 1, il circuito risponde come un normale trigger bistabile, diventando trasparente per gli stati di impostazione e reset.

Questo ingresso C aggiuntivo può anche essere collegato all'uscita del generatore di frequenza di clock, formando quindi un flip-flop RS sincrono. Pertanto, questo schema funziona come un "bistabile" trigger bistabile standard, ma le uscite sono attivate solo quando il livello 1 viene inviato all'ingresso C e sono disabilitate quando viene visualizzato un livello zero logico.

Trigger Registers

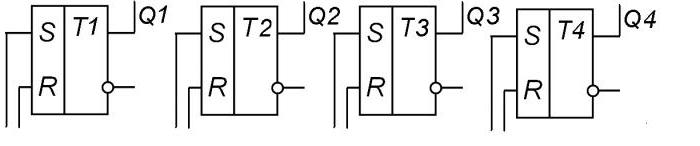

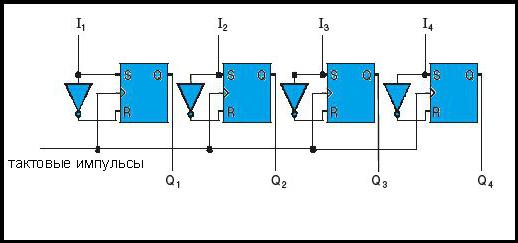

Un trigger RS può memorizzare 1 bit di informazioni digitali. Se è necessario memorizzare più bit, ad esempio una parola binaria digitale di più bit binari (in microcontrollori, solitamente 8 o 16), i trigger possono essere collegati in parallelo, formando registri. Questi sono i dispositivi più semplici per la memorizzazione temporanea di un insieme di cifre digitali binarie in cui ciascun trigger memorizza il valore di una cifra (0 o 1. cioè, un bit). Quindi, il registro a 4 bit mostrato di seguito sui flip-flop RS contiene quattro flip-flop separati.

Qualsiasi numero binario da (0000) 2 a (1111) 2 può essere memorizzato in questo registro semplicemente impostando o resettando il trigger corrispondente. Supponiamo che il primo trigger sia impostato (Q1 = 1), il secondo sia resettato (Q2 = 0), anche il terzo sia resettato (Q3 = 0) e il quarto sia impostato (Q4 = 1). Quindi il numero binario scritto nel registro sarà (1001) 2.

Oltre ai registri paralleli destinati alla memorizzazione di parole digitali, i cosiddetti registri di spostamento vengono fatti su flip-flop RS, in cui le cifre della parola digitale successivamente con l'arrivo di ciascun impulso di orologio vengono spostate di un bit verso sinistra o verso destra. Di seguito viene mostrato un diagramma di tale dispositivo su trigger sincroni.

Tali registri vengono utilizzati nei circuiti di interfaccia seriale, quando le parole digitali provenienti dal controllore di controllo vengono trasferite un po 'alla linea di comunicazione.